마이크로프로세서 : SPI (Serial Peripheral Interface) / ATmega128

글 작성자: _rian

SPI란?

SPI allows high-speed synchronous data transfer between ATmega128 and peripheral devices or between several AVR devices.

SPI는 동기식 데이터가 빠른 속도로 ATmega 128과 주변 장치, 또는 다른 AVR 디바이스 사이의 전송을 가능하게한다.

SPI의 특징

- 양방향 통신 가능하다. (Full duplex), 3개의 동기식 데이터전송 선이 있다. (clock, 보내는 데이터, 받는 데이터)

- 마스터-슬레이브 동작을 한다. (master or slave operation)

- 데이터 전송시 LSB를 먼저할지 MSB를 먼저할지 선택 가능하다.

- 7개의 전송 속도를 선택할 수 있다.

- 데이터 충돌이 일어났을 때 보호한다.

- Idle(sleep mode)에서 깨어난다.

- 2배속 가능하다.

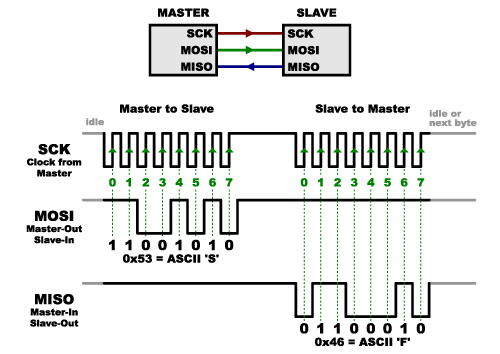

Interconnection between Master and Slave with SPI

상호연결 시스템에서는 2개의 shift register와 1개의 master clock generator가 있다.

데이터 통신 절차는 아래와 같다.

-

마스터가 Slave Select (SS)를 0으로 clear한다. (SS는 active low)

-

master와 slave 모두 각각의 shift register에 전송될 데이터를 준비한다.

-

master가 SCK 라인을 통해 clock(SCK)을 발생시키고 데이터를 교환한다.

-

데이터는 Master Out - Slave In (MOSI)라인과 Slave Out - Master In (MISO)라인을 통해 옮겨진다.

-

각 데이터 패킷들의 전송이 끝나면, 마스터는 SS 를 다시 1로 set 한다.

SPI 관련 레지스터들

1. SPI Control Register - SPCR

- Bit 7 (SPIE) : SPI의 인터럽트를 가능하게 한다. (SPI Interrupt Enable)

- Bit 6 (SPE) : SPI 통신을 가능하게 한다. (SPI Enable)

- Bit 5 (DORD) : 데이터 전송 순서를 정한다. (Data Order)

DORD = 1 ; 데이터 워드의 LSB 먼저 전송된다.

DORD = 0 ; 데이터 워드의 MSB 먼저 전송한다. - Bit 4 (MSTR) : master 할지 slave 할 지 선택한다. (Master/Slave Select)

MSTR = 1 ; Master SPI mode

MSTR = 0 ; Slave SPI mode - Bit 3 (CPOL) : Clock의 극성을 정한다.

CPOL = 1 ; SCK는 idle 상태일 때 1

CPOL = 0 ; SCK는 idle 상태일 때 0 - Bit 2 (CPHA) : Clock Phase 결정 => 데이터가 leading edge와 trailing edge중 어디에서 sample과 setup이 일어날 지 결정

CPHA = 1 ; Sample - leading edge / Setup - Trailing edge

CPHA = 0 ; Sample - trailing edge / Sample - leading edge - Bit 1, 0 (SPR1, SPR0) : 클럭 속도를 결정하는 비트

( 이 비트들은 뒤에 나오는 SPI2X와 함께 frequency를 설정할 때 사용한다. 내용은 아래 표에 있다.)

2. SPI Status Register - SPSR

- Bit 7 (SPIF) : SPI 인터럽트 플래그 - 통신이 끝나면 1로 세트한다.

- Bit 6 (WCOL) : Write COLlision flag - 데이터 충돌이 일어나면 세트한다.

- Bit 0 (SPI2X) : 마스터 모드에서 SPI의 전송 속도가 두배가 된다. (Double SPI Speed bit)

3. SPI Data Register - SPDR

- SPDR을 쓰는 것은 데이터 전송의 시작을 의미한다.

- SPDR을 읽는 것은 shift 레지스터가 읽을 버퍼를 받게 한다.