다중-버스 다중 프로세서 시스템 - 크로스바 네트워크, 다중-버스, 계층 버스 구조

다중-버스 다중 프로세서 시스템

단일 공유-버스 시스템의 버스 경합에 의한 지연을 줄이기 위하여 연결 통로를 제공하기 위한 시스템 구조이다. 종류는 아래와 같다.

- 크로스바 네트워크 (crossbar network) : 프로세서와 기억장치 모듈들 간에 완전 연결 (full connection)을 제공

- 다중-버스 구조(multiple-bus structure) : 공유 버스의 수가 두 개 혹은 그 이상이지만, 프로세서 수보다는 더 적은 구조

- 계층 버스 (hierarchical bus) 구조 : 버스의 역할(용도)이 서로 다른 계층적 구조의 다중-버스 구조

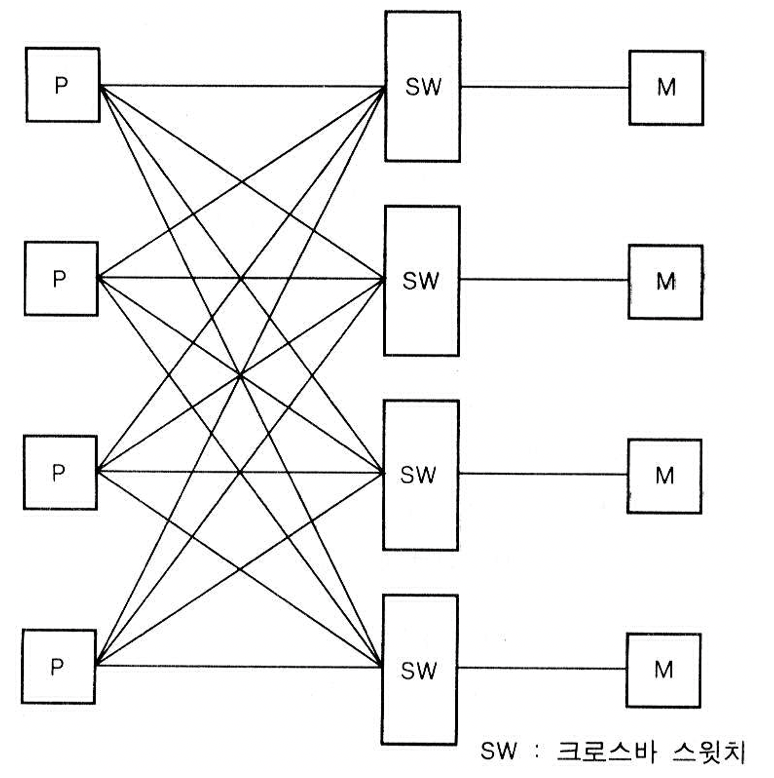

1. 크로스바 네트워크

- Carnegi-Mellon(멜론..!) 대학에서 연구용으로 개발한 C.mmp 시스템에서 처음 사용되었다.

- 시스템 요소들(프로세서, 기억장치 모듈) 간에 한 개씩의 별도 경로 존재함. -> 경로에 대한 경합으로 인한 지연이 없음.

프로세서와 스위칭 소자간의 채널 구성

- 데이터 버스

- 기억장치 주소

- 기억장치 제어(읽기/쓰기) 신호

- 기억장치 엑세스 요구 (REQ) 및 승인 (GRANT) 신호

채널의 폭 (선의 수)

NxN 시스템에서 각 채널이 m개의 선들로 구성되는 경우, 전체 I/O 선들의 수의 수는 아래 식과 같다.

$${m \times (N \times N)} + m \times N = m(N^2 + N)$$

=> \( O(n^2) \) : 스위칭 소자 내부의 H/W와 I/O 선의 수는 \( N^2 \) 에 비례

문제점

- H/W 복잡 : 프로세서 수 및 기억장치 수가 각각 N 개라면, 필요한 스위칭 소자의 수는 $N^2$

- 두 개 이상의 프로세서들이 동일한 기억장치 모듈을 엑세스 하려는 경우에는 기억장치 충돌(memory conflict) 발생 -> 중재 필요

2. 다중 - 버스 시스템 구조

버스 수가 1개 보다 많고 프로세서 수보다는 적으면 다중 버스 시스템이다.

공유 버스의 수를 증가시키면, 기억장치 대역폭 (memory bandwidth : 단위 시간당 기억장치 엑세스 수)가 증가해서 기억장치 엑세스의 동시성이 증가한다. 또한 시스템 결함 허용도(fault-tolerance)도 향상한다.

다중-버스 시스템 구조의 버스 중재

버스 중재 필요

- 동시에 기억장치를 엑세스 하려는 프로세서들의 수 > 버스의 수 => 버스 경합(bus contention)이 발생한다.

- 여러 프로세서들이 동시에 동일한 기억장치 모듈을 엑세스 하려 할 때 => 기억장치 충돌(memory conflict) 발생

1-of-N 중재기 (N=프로세서 수)

- 기억장치 모듈에 대한 중재 수행

- 각 모듈 당 한개씩, 전체 M개 (기억장치 모듈 수만큼) 필요

B-of-M 중재기 (B:버스 수, M : 기억장치 모듈 수)

- 버스들에 대한 중재 수행

- 1-of-N 중재기에 이해 기억장치 충돌이 해결된 버스 요구들에게 버스를 할당

- 시스템 내에 한개만 필요

버스 수의 변화에 따른 기억장치 대역폭

버스 수가 증가하더라도, 버스 대역폭이 선형적으로 증가하지 못하는 이유

- 버스 경합 (버스 수가 적은 시스템)

- 기억장치 충돌 (버스의 수가 많은 시스템)

- 기억장치 요구율 (memory request rate)이 충분히 높지 않은 경우

결국.. 크로스바 네트워크의 경우에 버스의 수가 절반인 다중-버스 시스템보다 성능이 약간 더 높을 뿐...

3. 계층-버스 시스템 구조

버스들이 계층적으로 접속되도록 하고, 각 계층의 버스에 접속되는 시스템 요소들의 종류와 버스의 기능이 서로 다른 시스템 구조.

- 시스템 버스 / 지역 버스

- 시스텝 버스 / 입출력 버스

- 클러스터 간 버스 / 클러스터 버스 / 지역 버스

장점

- 프로세서와 기억장치 또는 입출력 채널 간의 통신량을 각 지역 버스들로 분산

- 시스템 버스의 통신량이 감소되므로 버스 경합에 따른 지연 시간 단축

지역성(locality)에 관한 고찰

- 프로세서가 원하는 데이터 또는 프로그램 코드의 기억장치 위치

- 엑세스 요구를 발생한 컴퓨터 모듈 내의 기억장치

- 같은 클러스터에 있는 다른 컴퓨터 모듈의 기억 장치

- 다른 클러스터에 있는 컴퓨터 모듈의 기억장치

- 데이터들이 프로세서와 가까운 위치에 있는 기억장치에 저장되어 있을수록 (즉, 지역성이 높을수록) 시스템 성능이 더 높아진다.

프로그램 저장 위치와 평균 명령어 실행 시간의 실험 결과

4. 계층적 캐시/버스 구조

같은 클러스터(cluster) 내의 여러 프로세서들이 2차 캐시(second-level cache)를 공유하는 구조

클러스터들은 클러스터간 버스(inter-cluster bus)를 통하여 통신한다.

(예) Encore Computer 사의 Ultramax 다중 프로세서 시스템

'Computer Engineering > 병렬 처리(Parallel Processing)' 카테고리의 다른 글

| [병렬 처리] 고성능 입출력 시스템 구조 (0) | 2019.06.20 |

|---|---|

| [병렬처리] 상호 연결망 구조 - 정적 상호 연결망의 종류 (0) | 2019.06.20 |

| 그래픽 처리 유니트 (GPU) - GPU의 개념과 CUDA 프로그래밍 (0) | 2019.06.20 |

| 단일-버스 다중프로세서 시스템(2) - 캐쉬 일관성 유지를 위한 버스 감시 매커니즘 (MESI protocol), 디렉토리 기반 캐쉬 프로토콜 (0) | 2019.06.18 |

| 단일-버스 다중프로세서 시스템(1) - 버스 중재 방식과 캐시 일관성 유지 방법 (0) | 2019.06.17 |

댓글

이 글 공유하기

다른 글

-

[병렬처리] 상호 연결망 구조 - 정적 상호 연결망의 종류

[병렬처리] 상호 연결망 구조 - 정적 상호 연결망의 종류

2019.06.20 -

그래픽 처리 유니트 (GPU) - GPU의 개념과 CUDA 프로그래밍

그래픽 처리 유니트 (GPU) - GPU의 개념과 CUDA 프로그래밍

2019.06.20 -

단일-버스 다중프로세서 시스템(2) - 캐쉬 일관성 유지를 위한 버스 감시 매커니즘 (MESI protocol), 디렉토리 기반 캐쉬 프로토콜

단일-버스 다중프로세서 시스템(2) - 캐쉬 일관성 유지를 위한 버스 감시 매커니즘 (MESI protocol), 디렉토리 기반 캐쉬 프로토콜

2019.06.18 -

단일-버스 다중프로세서 시스템(1) - 버스 중재 방식과 캐시 일관성 유지 방법

단일-버스 다중프로세서 시스템(1) - 버스 중재 방식과 캐시 일관성 유지 방법

2019.06.17